| Brief Description | |

|---|---|

|

Files:

\examples\Processing\Geometry\TapGeometrySorting\TapSorting_2X_1Y.va |

|

|

Default Platform: mE5-MA-VCL |

|

|

Short Description Sorting of Camera Link Taps |

|

Taps are geometric zones on a camera sensor. The pixels of a frame are transmitted pixel by pixel to the frame grabber in sequential order from the taps. The pixels can be transferred in parallel from these taps. In Camera Link base configuration the number of taps transferred at the same clock cycle are 1 to 3, in medium configuration 3 or 4 and in full configuration 8 or 10. The geometric arrangement of the taps depends on the sensor model. Depending on this order, the pixels in the acquired image need to be resorted in order to achieve an image, which mirrors reality. To describe tap geometry configuration of a camera a naming convention

is used. Hereby  are the number of taps in horizontal and vertical direction. The number of consecutive pixels

in X and Y direction, which are transferred simultaneously from a tap are

are the number of taps in horizontal and vertical direction. The number of consecutive pixels

in X and Y direction, which are transferred simultaneously from a tap are  .

.

can be named "E", "M" or "R". "E" indicates, that the readout per taps starts from both ends of pixel lines/columns.

"M" means, that the pixel extraction starts from the middle of line. "R" shows, that pixel extraction starts at the right

side of each tap. In table 24

the pixel positions in horizontal and vertical direction for an image with width "w" and "height" h for specific tap geometries

are listed.

can be named "E", "M" or "R". "E" indicates, that the readout per taps starts from both ends of pixel lines/columns.

"M" means, that the pixel extraction starts from the middle of line. "R" shows, that pixel extraction starts at the right

side of each tap. In table 24

the pixel positions in horizontal and vertical direction for an image with width "w" and "height" h for specific tap geometries

are listed.

| Tap Geometry | X Start | X End | X Step | Y Start | Y End | Y Step | |

|---|---|---|---|---|---|---|---|

| 2X-1Y | Tap 1 | 1 | w/2 | 1 | 1 | h | 1 |

| Tap 2 | w/2+1 | w | 1 | 1 | h | 1 | |

| 2XE-1Y | Tap 1 | 1 | w/2 | 1 | 1 | h | 1 |

| Tap 2 | w | w/2+1 | 1 | 1 | h | 1 | |

| 1X-2Y | Tap 1 | 1 | w | 1 | 1 | h/2 | 1 |

| Tap 2 | 1 | w | 1 | h/2+1 | h | 1 | |

| 2X-2Y | Tap 1 | 1 | w/2 | 1 | 1 | h/2 | 1 |

| Tap 2 | w/2+1 | w | 1 | 1 | h/2 | 1 | |

| Tap 3 | 1 | w/2 | 1 | h/2+1 | h | 1 | |

| Tap 4 | w/2+1 | w | 1 | h/2+1 | h | 1 | |

| 2X-2YE | Tap 1 | 1 | w/2 | 1 | 1 | h/2 | 1 |

| Tap 2 | w/2+1 | w | 1 | 1 | h/2 | 1 | |

| Tap 3 | 1 | w/2 | 1 | h | h/2+1 | 1 | |

| Tap 4 | w/2+1 | w | 1 | h | h/2+1 | 1 | |

| 8X-1Y | Tap 1 | 1 | w/8 | 1 | 1 | h | 1 |

| Tap 2 | w/8+1 | 1/4 w | 1 | 1 | h | 1 | |

| Tap 3 | 1/4 w +1 | 3/8 w | 1 | 1 | h | 1 | |

| Tap 4 | 3/8 w +1 | 1/2 w | 1 | 1 | h | 1 | |

| Tap 5 | 1/2 w +1 | 5/8 w | 1 | 1 | h | 1 | |

| Tap 6 | 5/8 w +1 | 3/4 w | 1 | 1 | h | 1 | |

| Tap 7 | 3/4 w +1 | 7/8 w | 1 | 1 | h | 1 | |

| Tap 8 | 7/8 w +1 | w | 1 | 1 | h | 1 | |

| 10X-1Y | Tap 1 | 1 | w/10 | 1 | 1 | h | 1 |

| Tap 2 | w/10+1 | 1/5 w | 1 | 1 | h | 1 | |

| Tap 3 | 1/5 w +1 | 3/10 w | 1 | 1 | h | 1 | |

| Tap 4 | 3/10 w +1 | 2/5 w | 1 | 1 | h | 1 | |

| Tap 5 | 2/5 w +1 | 1/2 w | 1 | 1 | h | 1 | |

| Tap 6 | 1/2 w +1 | 3/5 w | 1 | 1 | h | 1 | |

| Tap 7 | 3/5 w +1 | 7/10 w | 1 | 1 | h | 1 | |

| Tap 8 | 7/10 w +1 | 4/5 | 1 | 1 | h | 1 | |

| Tap 9 | 4/5 w +1 | 9/10 | 1 | 1 | h | 1 | |

| Tap 10 | 9/10 w +1 | w | 1 | 1 | h | 1 |

Table 24. Examples of tap geometries

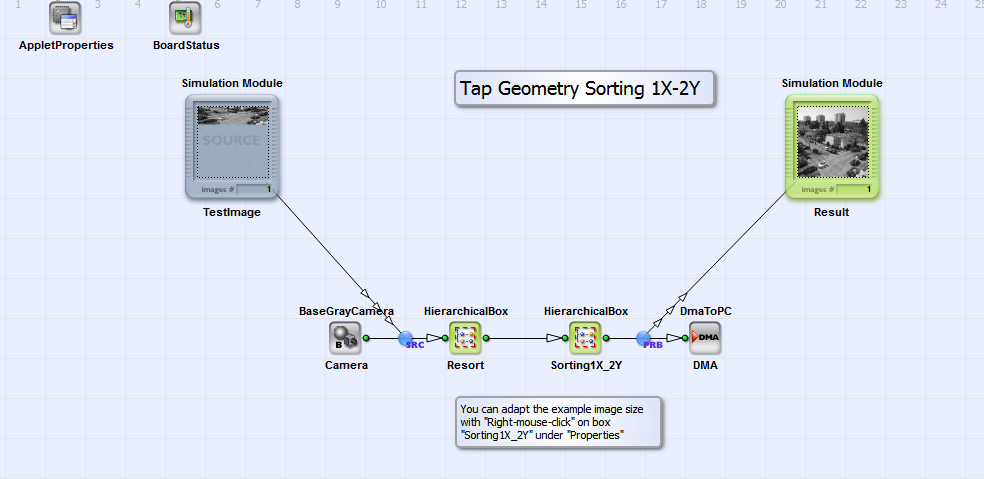

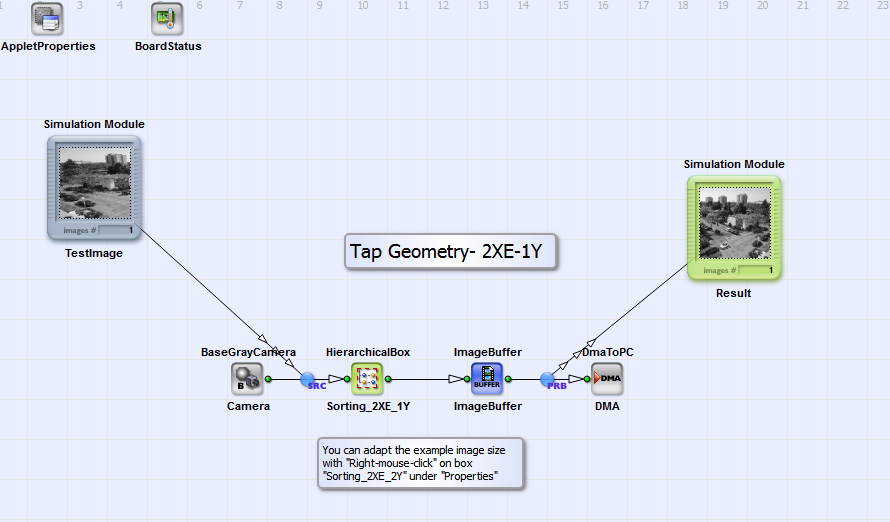

The sorting of the tap geometry modi described above is implemented in seven seperate Visual Applets designs. The designs can be used as part of image processing designs. For the simulation and test of the tap geometry sorting you find example images under \examples\Processing\Geometry\TapGeometrySorting\TestImages. The implementation algorithm differs from design to design to find the best balance between complexity and resource efficiency of the implementation. The simplest way to realize tap geometry sorting in horizontal direction is realized in the designs "TapSorting_2X_1Y.va" and "TapSorting_2XE_1Y.va". You can see the basic design structure of "TapSorting_2XE_1Y.va" in Fig. 363.

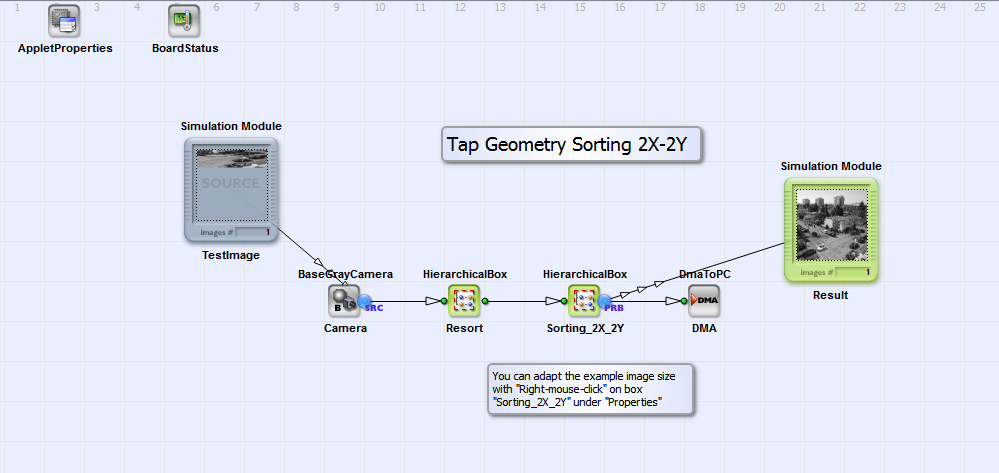

The pixels of the two taps "2X" in horizontal direction coming from a grayscale camera in Camera Link base configuration are split in two branches. The pixels of tap 2 are mirrored in horizontal direction in the HierachicalBox MirroredLine using operator LineMemory. The pixels of the two taps are then inserted line by line to a new image. Two sequential lines are then combined to one bigger line. This image is the output image with the correct tap geometry: The pixels of tap 1 are in the left half of the result image, whereas the pixels of tap 2 are in the right half in reverse order due to mirroring. The design structure and algorithm of "TapSorting_2X_1Y.va" is analog to the one of "TapSorting_2XE_1Y.va" but without the mirroring of the pixels of tap 2. The designs "TapSorting_1X_2Y.va", "TapSorting_2X_2Y.va" and "TapSorting_2X_2YE.va" have one or two taps in horizontal ("1X" or "2X") and two taps in vertical direction ("2Y" and "2YE") . The most efficient way of tap sorting is here using operator FrameBufferRandomRead. You can see the basic design structure of "TapSorting_2X_2Y.va" in Fig. 364. The design structures of "TapSorting_1X_2Y.va" and "TapSorting_2X_2YE.va" are equivalent.

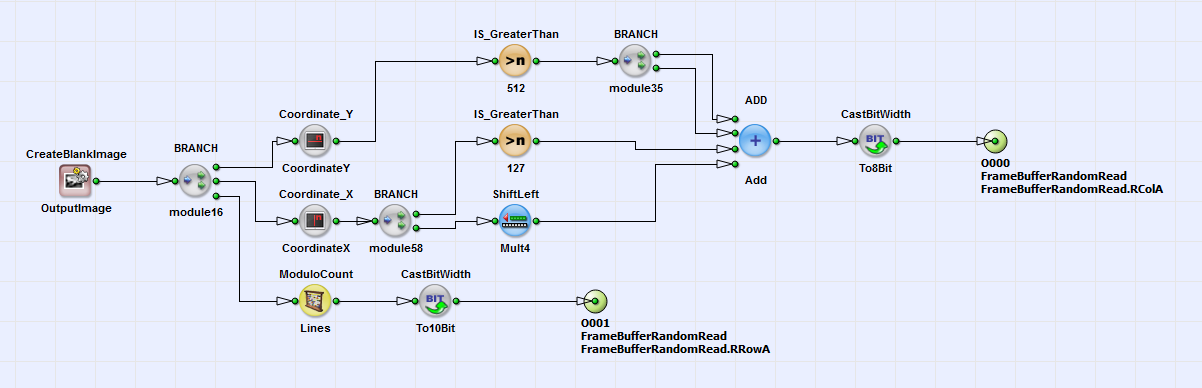

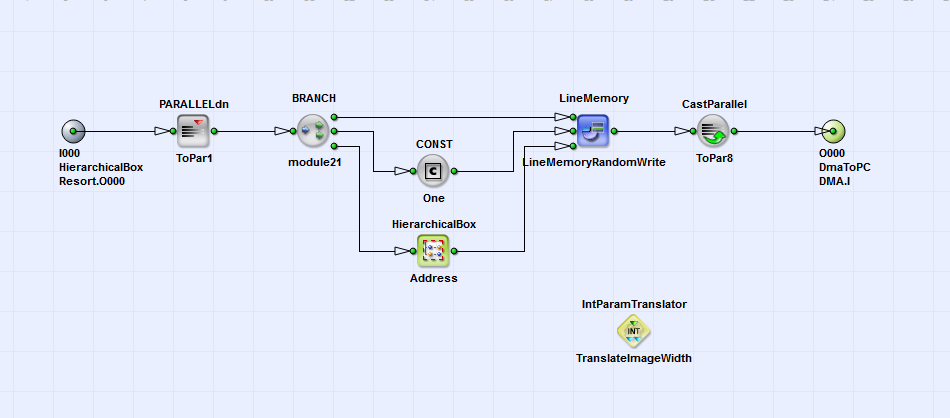

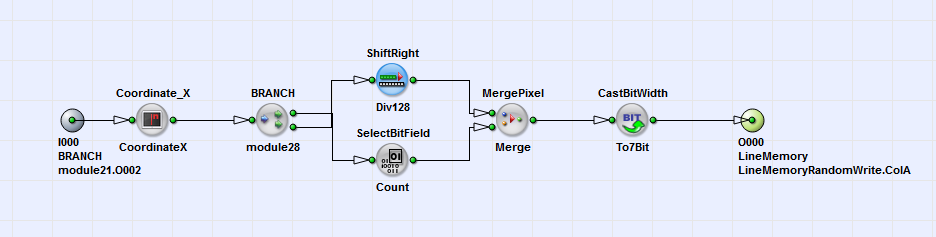

The pixels transferred from a camera in camera link base configuration are rearranged in their order in the HierarchicalBox Resort. Here four pixels of the same tap are merged to one pixel. Tap 1 to Tap 2 ("TapSorting_1X_2Y.va") or to Tap 4 ("TapSorting_2X_2Y.va" and "TapSorting_2X_2YE.va") are merged in parallel. Via the operator FrameBufferRandomRead with subsequent reinterpretation of the pixel depth (operator CastParallel) the pixels of the camera taps are positioned correctly in the result image. The correct address input for FrameBufferRandomRead is implemented in box Address. Here the designs differ in detail in dependence on the tap geometry used but follow the same principle. In Fig. 365 you can see the address generation for the design "TapSorting_2X_2Y.va".

With operators CoordinateX, CoordinateY, ModuloCount and IS_GreaterThan the corresponding positions in the input image for each pixel in the output image are evaluated.

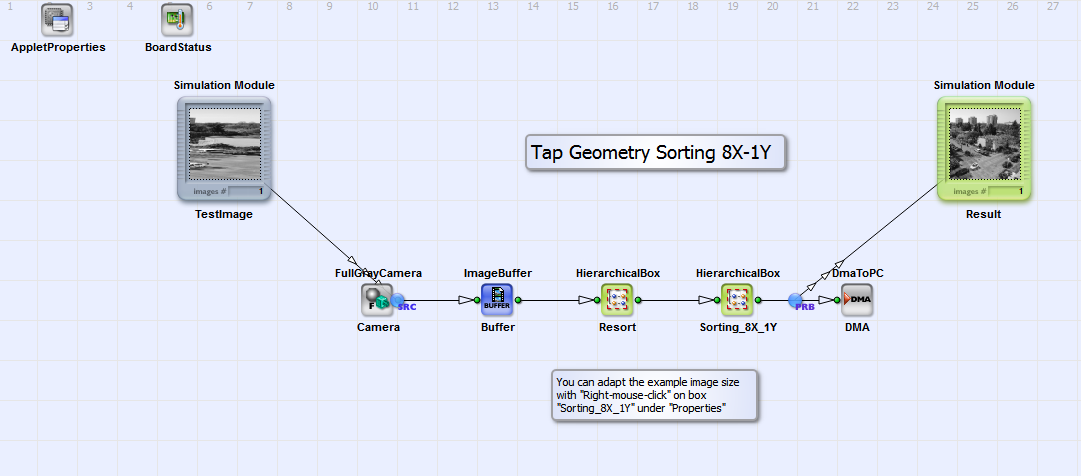

For the sorting of the tap geometry of "8X-1Y" and "10X-1Y" in the designs "TapSorting_8X_1Y.va" and "TapSorting_10X_1Y.va" operator LineMemory is used. You can see the basic design structure of "TapSorting_8X_1Y.va" in Fig. 366. The design structure of "TapSorting_10X_1Y.va" is equivalent.

The pixels of the eight or ten horizontal taps are rearranged in the HierarchicalBox Resort. Eight pixels of the same tap each are merged to one pixel with bit depth 64 bit. The eight or ten taps are merged in parallel. The correct address in the input image for each output pixel is then calculated in the HierachicalBox Sorting8X1Y (see Fig. 367).

You can see the the address generation of box Address in Fig. 368.

Prev

Prev